Questa Verification Management

Overview

Verification management means balancing various tools and techniques to get to closure, often with an infrastructure built on home-grown scripting and lots of manual maintenance. As verification complexity ascends, so, too, does the need for a more flexible automated solution.

When verification is not under control, project schedules slip, quality is jeopardized and the risk of re-spins soars. What’s required is a common platform and environment that provides all parties – system architects, software engineers, designers and verification specialists – with real-time visibility into the project. And not just to the verification plan, but also to the specifications and the design, both of which change over time. There are three dimensions to any IC design project: the process, the tools and the data. Questa offers a comprehensive approach to the problem with its verification management option that handles all within a scalable and modular solution.

Introducing Questa Verification Management

Questa Verification Management efficiently ties all verification-related tasks together and gives all parties — system architects, software engineers, designers and verification specialists — real-time visibility into the project. This visibility helps to hit market windows on schedule, manage risk and improve throughput and debug turnaround times.

Automated Productivity

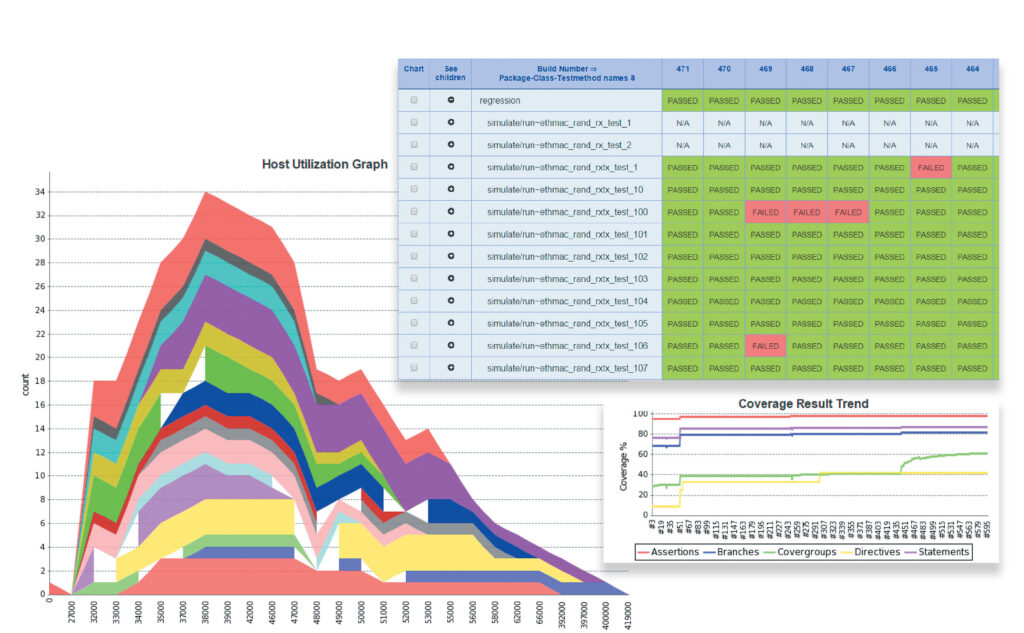

Questa’s verification run manager provides project consistency through broad automation. An intuitive web dashboard lets teams observe and analyze project results and trends, allowing dispersed project teams to improve time to coverage and time to next bug, and enhancing their ability to accurately estimate the time to completion.

High Performance, High Capacity

Built on multiple powerful technologies, the Questa Verification Platform enables teams to select the best application or tool for the job, and combine results from all the engines to dynamically track the progress of the entire verification program, dramatically increasing productivity and more efficiently managing resources.

Questa’s verification management capabilities are built upon the Unified Coverage Database (UCDB). The UCDB captures any source of coverage data generated by verification tools and processes; Questa and ModelSim use this format natively to store code coverage, functionality coverage and assertion data in all supported languages.

UCDB also enables the capability to capture information about the broader verification context and process, including which verification tools were used and even which parameters constrained these tools.

The result is a rich verification history, one that tracks user information about individual test runs and also shows how tests contribute to coverage objects.

Process Management

Verification is driven by requirements concerning both the functionality of the final product and the intended methods of testing this functionality. By providing tools to import verification or test plans and then guide the overall process, Questa verification management helps deal with this complexity and shepherd a project toward electronic closure. It also provides the ability to store snapshots of data across the lifetime of a project, which helps to concentrate efforts where they are most needed.

Key Benefits

- Integrated verification management and analysis

- Visibility to hit market windows on schedule

- Reduce the volume of data and track project progress

- Manage the risk to keep resources on track

- Reduce maintenance and improve automation

- Jump start the debug process

Interested in Questa Verification Management?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

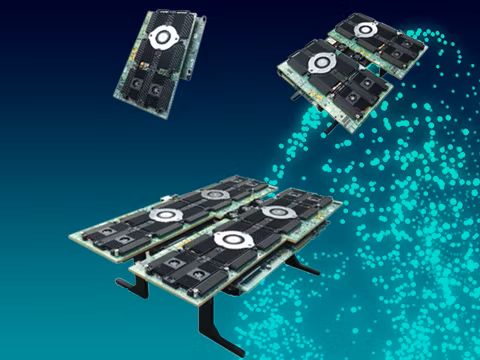

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.