Questa Advanced Simulator

Overview

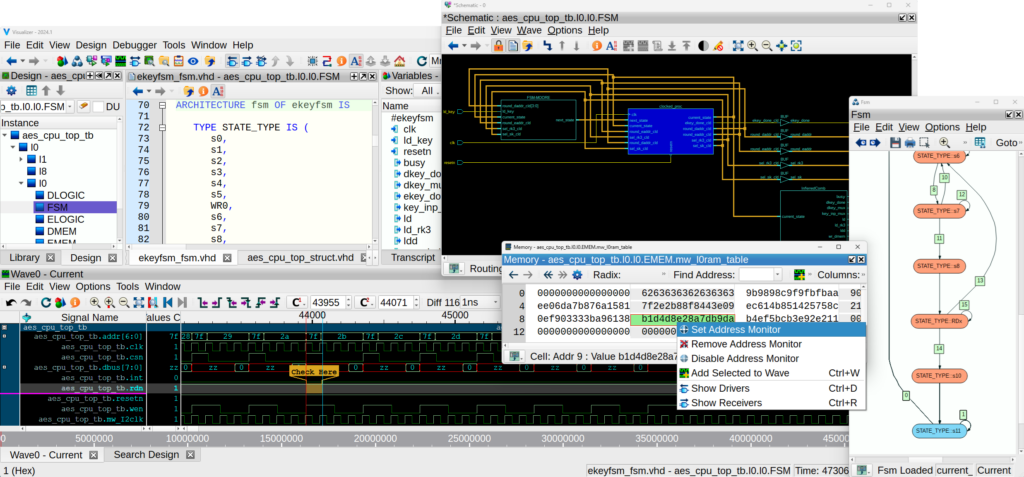

The Questa Advanced Simulator combines high performance, high capacity simulation with unified debug and functional coverage for complete native support of Verilog, SystemVerilog, VHDL, SystemC, SVA, UPF and UVM.

Questa’s Core Simulation and Debug Engine

QuestaSim is the core simulation and debug engine of the Questa verification solution; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs.

The Questa Advanced Simulator achieves industry-leading performance and capacity, through very aggressive global compile and simulation optimisation algorithms for SystemVerilog and VHDL.

Introducing QuestaSim

The Questa simulator spans the levels of abstraction required for complex SoC and FPGA design and verification, from Transaction Level Modelling (TLM) through RTL, gates, and transistors. It has superior support of multiple verification methodologies including Assertion Based Verification (ABV), Open Verification Methodology (OVM) and Universal Verification Methodology (UVM) to increase testbench productivity, automation and reusability.

High Performance and Capacity

Using its advanced algorithms, the Questa Advanced Simulator can help you improve SystemVerilog and mixed VHDL / SystemVerilog RTL simulation performance by up to 10X. Questa also supports fast time-to-next simulation and effective library management while maintaining high performance with unique capabilities to pre-optimise and define debug visibility on a block by block basis enabling dramatic regression throughput improvements of up to 3X when running a large suite of tests.

Multi-Core Simulation

The Questa Advanced Simulator supports all design languages and constructs, and either automatically or manually partitions the design to run in parallel while maintaining a single database for debug and coverage.

Testbench Automation

The Questa Advanced Simulator supports the most comprehensive solutions for testbench automation in the industry, enabling automatic creation of complex, input-stimuli using SystemVerilog or SystemC Verification (SCV) library constructs, and combining these forms of stimulus generation with functional coverage to identify the functionality exercised by the automatically-generated stimulus.

Assertion Based Verification

Questa delivers a comprehensive, standards-based ABV solution, offering the choice of SystemVerilog, Property Specification Language (PSL), or both. To ease the adoption of ABV, Questa includes the Questa Verification Library (QVL), which is a comprehensive SystemVerilog assertion checker and monitor library. QVL Checkers cover a wide range of design properties and are optimised for formal verification and emulation, while QVL Monitors support a wide range of industry standard protocols for simulation.

Key Features and Benefits

- High-performance, multi-language engine for the most sophisticated regression suites

- Highly productive advanced verification solution with verification management for coverage closure of large, complex electronic systems

- Easy to use, fast time-to-debug through native assertions and a complete multi-abstraction and multi-language debug environment including transaction-level debug

- Constrained-random stimulus generation to automate test development

- Native advanced SystemVerilog testbench capabilities with OVM and UVM combined with unique debug function to ease the development and debug of advanced testbenches

Interested in QuestaSim?

Contact us to Learn More

The Verification Academy

The Verification Academy is a collection of free online courses, focusing on various key aspects of advanced functional verification.

Tools for Simulation & Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Questa Verification IP

Verification IP

Questa Verification IP (QVIP) improves quality and reduces schedule times by building protocol and methodology reusable components that support many industry standard interfaces.

ModelSim

HDL Simulation

ModelSim’s award winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design.