Questa Lint

Overview

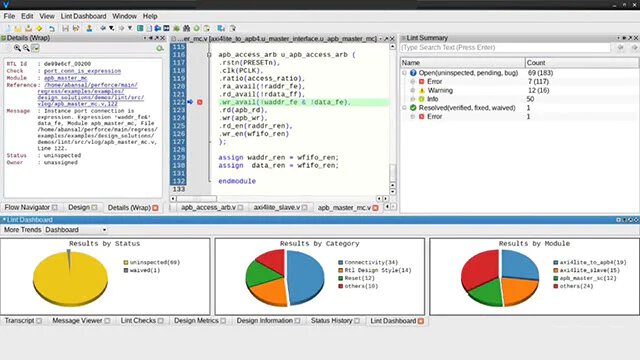

Questa Lint delivers verification automation for designers. Questa Lint produces intent and quality-focused insight at the design stage. Questa Lint’s metrics and quality scores are captured and trended over time to ensure that design stays clean.

Questa Lint provides actionable results with low noise. The linter reviews reported issues, then uses its deep understanding of every issue known to provide results different than inferred intent (as well as those known to cause false violations), to adapt the results. This results in reporting only the issues that need to be fixed, and in the order of those that matter most, resulting in actionable results and faster fix cycles.

Introducing Questa Lint

Mistakes happen, but finding and fixing issues late in programs increases overall program scope, as well as schedule and resource requirements. Competitive pressures push teams constantly to do more. Functional verification teams face significant challenges to build testbenches quickly, uncover design issues and enable rapid debug. Incomplete or incorrect bug fixes (or even a hurried introduction of new bugs) compound the problem.

Questa Lint provides a fast check of your RTL, without waiting for a testbench, looking for completeness and consistency issues. Using syntactic, semantic, stylistic, and structural analyses, the linter identifies issues when introduced, preventing issues from becoming more expensive to fix later. Results are presented in intuitive visualizations, with metrics and quality scores summarizing detailed information in an easy-to-use dashboard.

Out-of-the-box results

Questa Lint implements pre-configured methodologies for IP, SoC, and FPGA development to improve your team’s productivity from the start. Questa Lint also offers pre-built checksets for industry standards such as ISO 26262, DO-254, STARC. You can also configure your own methodologies and goals.

Adaptive insights

Discovering issues by applying deep learning of known issues, Questa Lint reports only the issues that are different from inferred intent and need attention. Questa Lint scores design quality to indicate which integrated IP blocks may cause issues later.

Ensure your design stays clean

Questa Lint integrates into popular Continuous Integration management tools, ensuring that throughout the development process, a design, once proven clean, remains that way.

From immediate results to custom methodologies

Architected to provide immediate out-of-the-box results, Questa Lint implements pre-configured methodologies for IP, FPGA or SoC development. Each of these methodologies offers an array of pre-defined readiness goals, such as floor-planning or synthesis readiness. In addition, there are pre-built checksets supporting industry standards such as DO-254, ISO-26262 or STARC. Once familiar with the tool, you can configure your own methodologies and checks to enable Questa Lint to enforce your development methodology, either through release-focused reviews or through continuous integration flows.

Interested in Questa Lint?

Contact us to Learn More

Software for IC Verification

QuestaSim

Simulation and Debug

Combines high performance and capacity simulation with unified advanced debug and functional coverage for the most complete native support of Verilog, SystemVerilog, VHDL, …

Catapult HLS

HLS and Verification

Industry leading C++ / SystemC High-Level Synthesis with Low-Power estimation / optimization. Design checking, code, and functional coverage verification plus formal make HLS more than ….

Questa Inspect

Static RTL Bug Hunting

A fully-automatic formal bug hunting app that finds deeply hidden bugs due to common RTL coding errors, Inspect makes it possible to eliminate a wide range of bugs without a testbench.

Questa CDC

CDC Verification

Questa CDC finds errors using structural analysis to detect clock-domains, synchronisers, and low power structures via the UPF. It then generates assertions and metastability models for …

Questa Lint

Static RTL Verification

Questa Lint provides adaptive, integrated insight to the designer to ensure that the quality requirements and intent are met. Pre-configured methodologies provide immediate, intuitive feedback …

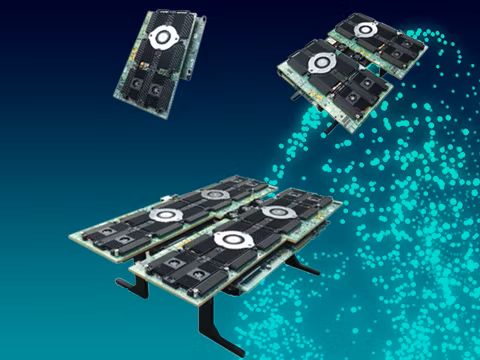

Veloce proFPGA

Hardware-Assisted Verification

The Veloce proFPGA system architecture offers best-in-class modularity, scalability, flexibility and portability to serve the verification requirements of today’s hardware and software engineers.